Introduction 0000 000 00 0 00 Generating Complete Tests

Example

イロト 不得 とくほ とくほう

3

# Generating Complete and Finite Test Suite for ioco Is It Possible?

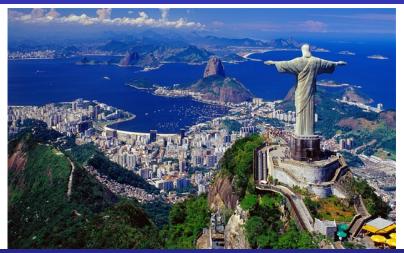

Adenilso Simao Alexandre Petrenko

adenilso@icmc.usp.br

April/06/2014 9th Workshop on Model-Based Testing Grenoble, France

Adenilso Simao Alexandre Petrenko

| Introduction | IOTS | Generating Complete Tests | Example | Conclusion |

|--------------|------|---------------------------|---------|------------|

| 0000         |      | 000                       |         |            |

|              |      |                           |         |            |

| 00           |      | 000000                    |         |            |

|              |      |                           |         |            |

#### Introduction

Adenilso Simao Alexandre Petrenko

| Introduction |  |

|--------------|--|

|              |  |

|              |  |

| 00           |  |

0 00 Generating Complete Tests

Example

Conclusion

#### Introduction (II)

ヨー つくで

Adenilso Simao Alexandre Petrenko Generating Complete and Finite Test Suite for ioco

| Introduction |  |

|--------------|--|

|              |  |

|              |  |

| 00           |  |

0 00 Generating Complete Tests

Example

Conclusion

#### Introduction (III)

Adenilso Simao Alexandre Petrenko

| Introduction | IOTS | Generating Complete Tests | Example | Conclusion |

|--------------|------|---------------------------|---------|------------|

| 0000         |      | 000                       |         |            |

| 000          | 00   |                           |         |            |

|              |      |                           |         |            |

|              |      |                           |         |            |

#### Introduction (IV)

Adenilso Simao Alexandre Petrenko

| Introduction<br>● ○ ○ ○<br>○ ○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|--------------------------------|------------------------|------------------------------------------------------|---------|------------|

| Context                        |                        |                                                      |         |            |

| Context                        |                        |                                                      |         |            |

- Model Based Testing

- Modeling

- Test Generation

- Test Execution

- Test Analysis

| Introduction<br>○●○○<br>○○○<br>○○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>000000<br>000000 | Example | Conclusion |

|-----------------------------------|------------------------|------------------------------------------------------|---------|------------|

| Context                           |                        |                                                      |         |            |

| Modeling                          |                        |                                                      |         |            |

- Many different models

- State based

- Finite State Machines (FSM)

- Input/Output Transition System (IOTS)

| Introduction<br>○○●○<br>○○ | <b>IOTS</b><br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|----------------------------|-------------------|------------------------------------------------------|---------|------------|

| Context                    |                   |                                                      |         |            |

- Tests should be

- Sound

- Every implementation that fails is indeed faulty

- Exhaustive (for a given fault domain)

- Every fault implementation fails

- Test generation can be

- On the fly

- Preset

- Adaptive

| Introduction<br>○○○●<br>○○○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------|------------------------|------------------------------------------------------|---------|------------|

| Context                     |                        |                                                      |         |            |

| Test Exec                   | cution                 |                                                      |         |            |

- Interaction with system

- For FSM, it is straightforward

- For IOTS, it can be

- Synchronous

- Controllability problems

- Input/Output Conflict

- Asynchronous

- Decidability problems

| Introduction<br>○○○○<br>○○○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------|------------------------|------------------------------------------------------|---------|------------|

| Problem Statement           |                        |                                                      |         |            |

|                             |                        |                                                      |         |            |

#### Problem Statement

- Is it possible to generate complete (sound and exhaustive) test suites for IOTS?

- A la Finite State Machines

- Conformance relation

- ioco

| Introduction<br>○○○○<br>○●○<br>○○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------------|------------------------|------------------------------------------------------|---------|------------|

| <b>D</b> 11 OL 1                  |                        |                                                      |         |            |

Problem Statement

# Problem Statement (II)

- It is known that:

- It is decidable for FSMs

- Many methods available

- It is undecidable whether two IOTSs are equivalent, when interacting via FIFO queues (Hierons, 2012)

- In the general case

- But,

- Is there a subclass of IOTS models for which can generate complete test suites?

- Under which assumptions?

| Introduction<br>○○○○<br>○○●<br>○○ | <b>IOTS</b><br>0<br>00 | Generating Complete Tests | Example | Conclusion |

|-----------------------------------|------------------------|---------------------------|---------|------------|

| Problem Statement                 |                        |                           |         |            |

|                                   |                        |                           |         |            |

## Existing solutions

- I/O conflicts yield uncontrollable tests

- Solved via FIFO queues (or ignored)

- Nondeterministic test suite generation

- Theoretically complete, but unbounded

| Introduction<br>○○○○<br>●O | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|----------------------------|------------------------|------------------------------------------------------|---------|------------|

| Summary of Results         |                        |                                                      |         |            |

| Summary                    | of Resul               | ts                                                   |         |            |

Test generation method which produces tests that are

- Finite (and bounded)

- Controllable

- Sound

- Exhaustive for a given class of faults

| Introduction<br>○○○○<br>○○○<br>○● | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------------|------------------------|------------------------------------------------------|---------|------------|

| Summary of Results                |                        |                                                      |         |            |

| Input Eag                         | er IOTS                |                                                      |         |            |

- The key assumption

- The implementation is assumed to be eager for inputs

- It solves conflicts favoring inputs over outputs

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------------|------------------------|------------------------------------------------------|---------|------------|

|                                   |                        |                                                      |         |            |

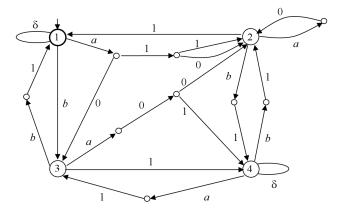

#### Input/Output Transition Systems

#### Definition

$(S, s_0, I, O, h_S)$ , where *S* is a finite set of states and  $s_0 \in S$ , is the initial state, *I* and *O* are disjoint sets of input and output actions, respectively, and  $h_S \subseteq S \times (I \cup O) \times S$  is the transition relation.

| Introduction<br>0000<br>000<br>00 | IOTS<br>●<br>○○ | Generating Complete Tests<br>000<br>0<br>000000<br>0 | Example | Conclusion |

|-----------------------------------|-----------------|------------------------------------------------------|---------|------------|

| Example                           |                 |                                                      |         |            |

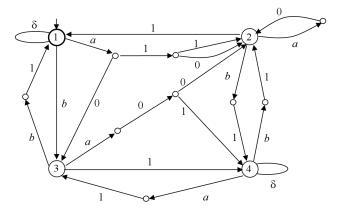

#### Example

◆□ → ◆□ → ◆ 三 → ◆ □ → ◆ ○ ◆ ○ ◆ ○ ◆ ○ ◆

Adenilso Simao Alexandre Petrenko

| Introduction<br>0000<br>000<br>00 | IOTS<br>○<br>●○ | Generating Complete Tests | Example | Conclusion |

|-----------------------------------|-----------------|---------------------------|---------|------------|

| Input/Output Conflicte            | •               |                           |         |            |

# Input/Output Conflicts

- Input states

- Only inputs are enabled

- Quiescent

- Bridge traces

- From input state to input states

- Quasi-stable state

- There is a conflict between inputs and outputs

| Introduction<br>0000<br>000<br>00 | IOTS<br>○<br>○● | Generating Complete Tests<br>000<br>0000000<br>0000000 | Example | Conclusion |

|-----------------------------------|-----------------|--------------------------------------------------------|---------|------------|

|                                   |                 |                                                        |         |            |

Input/Output Conflicts

#### Input/Output Conflicts (II)

◆□ > ◆□ > ◆豆 > ◆豆 > ̄豆 \_ 釣�(♡

Adenilso Simao Alexandre Petrenko

| Introduction | IOTS | Generating Complete Tests | Example | Conclu |

|--------------|------|---------------------------|---------|--------|

| 0000         |      | 000                       |         |        |

| 000          | õo   |                           |         |        |

| 00           |      | 000000                    |         |        |

|              |      |                           |         |        |

#### **Generating Complete Tests**

- HSI-method for FSMs

- Uses sets of distinguishing input sequences,

- Harmonized state identifiers, one per state

- Any two identifiers share an input sequence which distinguishes the two states

- Appended to state and transition covers

- Checks that every state of the implementation corresponds to some state of the specification

- Checks that every transition of the implementation corresponds to a transition of the specification

- Complete for a given fault domain

- All implementations which correspond to an FSM with at most a given number of states

lusion

Introduction 0000 000 000 0 00 Generating Complete Tests

### Generating Complete Tests (II)

- Inspired by HSI-method

- Fault domain

- All (input eager) IOTS with at most as many input states as the specification

- State reachability

- Transition coverage

- Bridge traces

- ▶ *Cov*(*s*,*x*)

- ▶ (*s*, *x*)-cover

- State distinguishability

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>● ○ ○<br>○<br>○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ | Example | Conclusion |

|-----------------------------------|------------------------|------------------------------------------------------------------------|---------|------------|

| State Reachability                |                        |                                                                        |         |            |

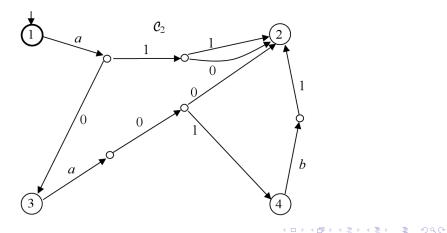

| State Rea                         | achability             |                                                                        |         |            |

- Guarantees that s is reached in any conforming implementation

- Preamble  $\mathcal{C}_s$  for state s

- A submachine of the specification

- Single-input

- Acyclic

- Output-preserving

- We propose an algorithm for computing preamble

| ntroduction | IOTS |

|-------------|------|

| 000         |      |

|             |      |

|             |      |

| Generating Complete Tests |  |

|---------------------------|--|

| 000                       |  |

|                           |  |

| 000000                    |  |

|                           |  |

Example

Conclusion

#### State Reachability

#### State Reachability (II)

Adenilso Simao Alexandre Petrenko

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>OO●<br>OOOOOOO<br>O | Example | Conclusion |

|-----------------------------------|------------------------|--------------------------------------------------|---------|------------|

| State Reachability                |                        |                                                  |         |            |

| State Rea                         | chability              | (111)                                            |         |            |

- Input state cover

- Set of preambles, one for each input state

- Transition cover

- Preambles of the state cover followed by bridge traces

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests | Example | Conclusion |

|-----------------------------------|------------------------|---------------------------|---------|------------|

| Transition Cover                  |                        |                           |         |            |

| Transitior                        | n Cover                |                           |         |            |

A transition cover V of S is the set of preambles of an input state cover chained with (s, x)-covers

◆□ ▶ ◆□ ▶ ◆ 三 ▶ ◆ 三 ● ● ● ● ●

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>00 | Generating Complete Tests<br>○○○<br>●○○○○○<br>○ | Example | Conclusion |

|-----------------------------------|-------------------|-------------------------------------------------|---------|------------|

| State Distinguishability          | /                 |                                                 |         |            |

| State Dist                        | inguishat         | oility                                          |         |            |

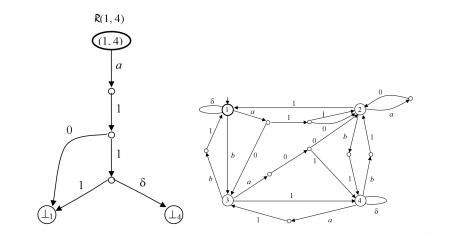

- Given two input states s<sub>1</sub> and s<sub>2</sub>, how to decide in which of the states the implementation is in

- ▶ Separator ℜ(s<sub>1</sub>, s<sub>2</sub>)

- Single-input acyclic machine

- Traces are disjoint

- Two sink states, one for each state (s<sub>1</sub> and s<sub>2</sub>)

- We propose an algorithm for generation of a separator

- Based on product machine

- Minimality

- There is a separator for each pair of states

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>○○○<br>○●○○○○○ | Example | Conclusion |

|-----------------------------------|------------------------|---------------------------------------------|---------|------------|

| State Distinguishabili            | ty                     |                                             |         |            |

#### Separators

Adenilso Simao Alexandre Petrenko

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>00 | Generating Complete Tests<br>○○○<br>○<br>○●○●○○○<br>○ | Example | Conclusion |

|-----------------------------------|-------------------|-------------------------------------------------------|---------|------------|

| State Distinguishabil             | ity               |                                                       |         |            |

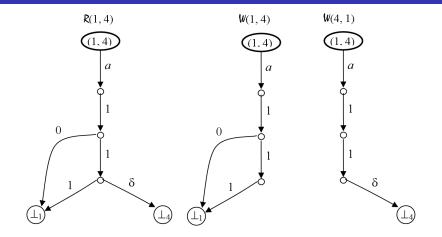

| Distinguis                        | hers              |                                                       |         |            |

- ▶ Distinguisher  $W(s_1, s_2)$

- Derived from  $\Re(s_1, s_2)$

- Removing one of the sink states

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>○○○<br>○○○○●○○<br>○ | Example | Conclusion |

|-----------------------------------|------------------------|--------------------------------------------------|---------|------------|

| State Distinguishabili            | ty                     |                                                  |         |            |

#### Distinguishers (II)

▲□▶▲圖▶▲≣▶▲≣▶ ≣ のへで

Adenilso Simao Alexandre Petrenko

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>00 | Generating Complete Tests<br>○○○<br>○<br>○○○●○<br>○ | Example | Conclusion |

|-----------------------------------|-------------------|-----------------------------------------------------|---------|------------|

| State Distinguishabil             | ity               |                                                     |         |            |

| State Ider                        | ntifiers          |                                                     |         |            |

- ► State identifier  $\mathcal{ID}(s)$

- Set of distinguishers

- One for each input state different from s

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>○○○<br>○○○○○○●<br>○ | Example | Conclusion |

|-----------------------------------|------------------------|--------------------------------------------------|---------|------------|

| State Distinguishabili            | ty                     |                                                  |         |            |

| Harmoniz                          | ed State I             | dentifiers                                       |         |            |

- Each pair of state identifiers has common prefix

- Long enough to distinguish the states

- HSI

| Introduction<br>0000<br>000<br>00 | <b>IOTS</b><br>0<br>00 | Generating Complete Tests<br>○○○<br>○<br>●<br>● | Example | Conclusion |

|-----------------------------------|------------------------|-------------------------------------------------|---------|------------|

| Complete Test Suite               |                        |                                                 |         |            |

| Complete                          | e Test Suit            | е                                               |         |            |

- The set of IOTSs obtained by chaining each IOTS from the input state cover and transition cover with a corresponding harmonized state identifier

- ▶  $D = \{ \mathbb{T} \mathbb{Q}_s \mathcal{R} \mid s \in sink(\mathbb{T}), \mathbb{T} \in (Z \cup V), \mathcal{R} \in \mathbb{T} D(s) \}, \text{ where }$

- sink(T) is the set of sink states of T

- Z is a state cover.

- V is a transition cover

- Complete with fail state

| Introduction | IOTS | Generating Complete Tests | Example | Conclusion |

|--------------|------|---------------------------|---------|------------|

| 0000         |      | 000                       |         |            |

| 000          | 00   |                           |         |            |

| 00           |      | 000000                    |         |            |

|              |      |                           |         |            |

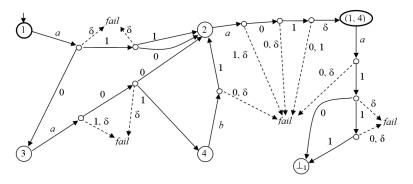

#### Example

► Test Case *TC*(C<sub>2</sub>Q<sub>2</sub>*Cov*(2, *a*)Q<sub>1</sub>*W*(1, 4)).

Adenilso Simao Alexandre Petrenko

| Introduction | IOTS | Generating Complete Tests | Example | Conclusion |

|--------------|------|---------------------------|---------|------------|

| 0000         |      | 000                       |         |            |

| 000          | 00   |                           |         |            |

| 00           |      | 000000                    |         |            |

|              |      |                           |         |            |

## Conclusion

- Generating Complete and Finite Test Suite for ioco: Is It Possible?

- (qualified) Yes, it is.

- For some IOTS

- All input states are reachable

- All input states are distinguishable

- There are harmonized state identifiers

- Under certain assumptions

- There is no more input states in the implementation than in the specification

- The implementation is eager for inputs

- We have proposed a method similar to HSI for FSM

| Introduction | IOTS | Generating Complete Tests | Example | Conclusion |

|--------------|------|---------------------------|---------|------------|

| 0000         |      | 000                       |         |            |

| 000          | 00   |                           |         |            |

| 00           |      | 000000                    |         |            |

|              |      |                           |         |            |

#### **Future Work**

Relax the constraints and assumptions

▲□▶▲圖▶▲≣▶▲≣▶ ≣ のQ@

Adenilso Simao Alexandre Petrenko

Introduction 0000 000 00 0 00 Generating Complete Tests

Example

イロト 不得 とくほ とくほう

3

# Generating Complete and Finite Test Suite for ioco Is It Possible?

Adenilso Simao Alexandre Petrenko

adenilso@icmc.usp.br

April/06/2014 9th Workshop on Model-Based Testing Grenoble, France

Adenilso Simao Alexandre Petrenko